According to DigiTimes, TSMC is accelerating orders with backend equipment suppliers as it starts an expansion plan for its chip-on-wafer-on-substrate (CoWoS) packaging capacity. The shortage of compute GPUs for artificial intelligence and high-performance computing, which Nvidia largely dominates, is mainly attributed to TSMC's limited CoWoS packaging production capabilities.

Reports suggest that TSMC has plans to increase its current CoWoS capacity from 8,000 wafers per month to 11,000 wafers per month by the end of 2023 and then to around 14,500 – 16,600 wafers by the end of 2024. Previously Nvidia was rumored to increase its CoWoS capacity to 20,000 wafers per month by the end of 2024. Remember that the information comes from unofficial sources and may be inaccurate.

Major tech giants like Nvidia, Amazon, Broadcom, Cisco, and Xilinx have all boosted their demand for TSMC's advanced CoWoS packaging and are consuming every wafer they can get. As a result, TSMC has been forced to renew orders for necessary equipment and materials, according to DigiTimes. The production of AI servers has significantly risen, fueling the already intense demand for these advanced packaging services.

Nvidia has already booked 40% of TSMC's available CoWoS capacity for the coming year. However, due to the severe shortage, Nvidia has started exploring options with its secondary supplier, placing orders with Amkor Technology and United Microelectronics (UMC), although these orders are relatively small, the report claims.

To cater to its increased CoWoS packaging needs, TSMC is partnering with multiple suppliers from around the globe, including U.S.-based Rudolph Technologies, Japan's Disco, and Germany's SUSS MicroTec, along with Taiwanese experts Grand Process Technology (GPTC) and Scientech. The suppliers are under pressure to provide almost 30 sets of relevant tools by mid-2024.

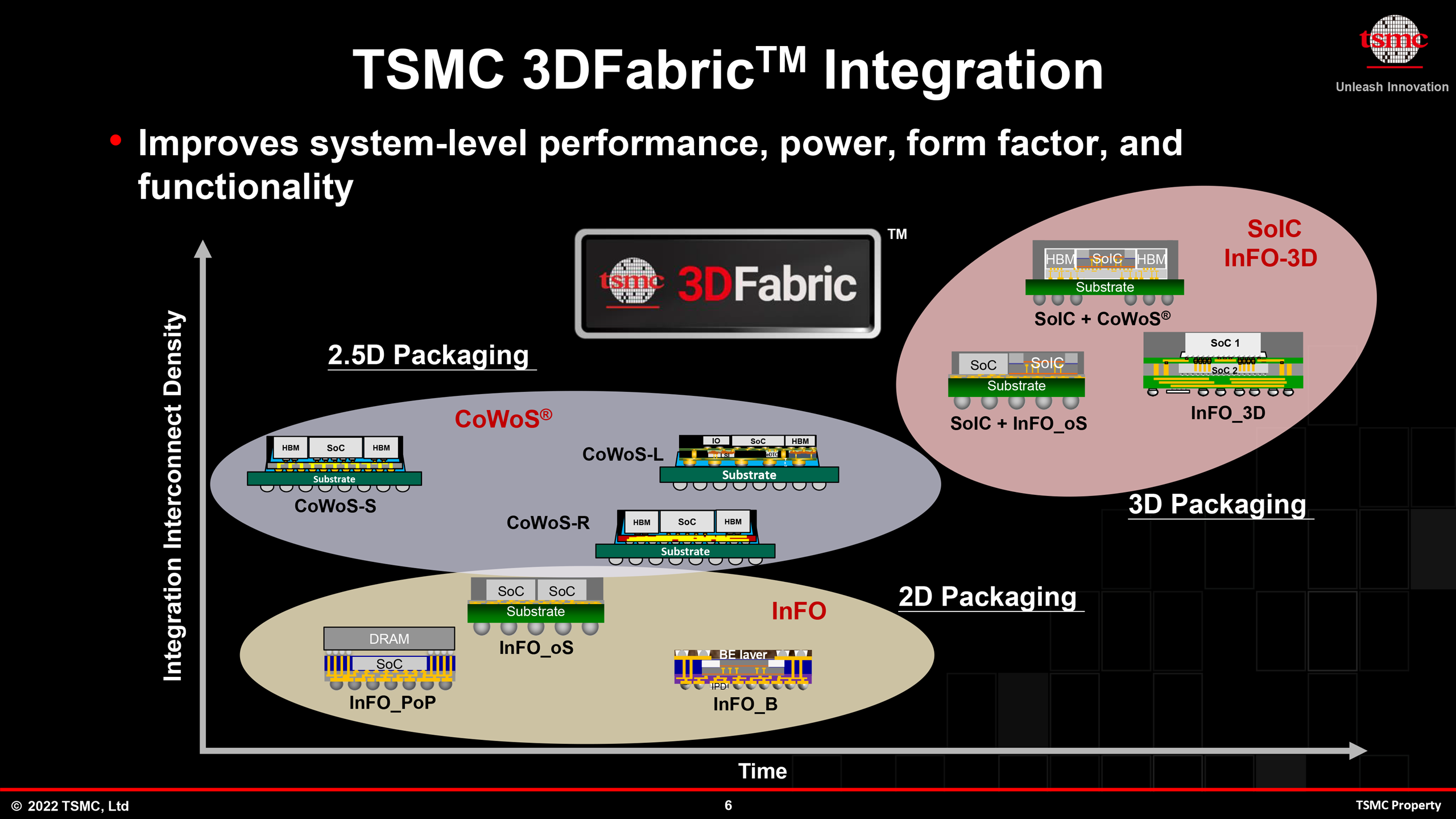

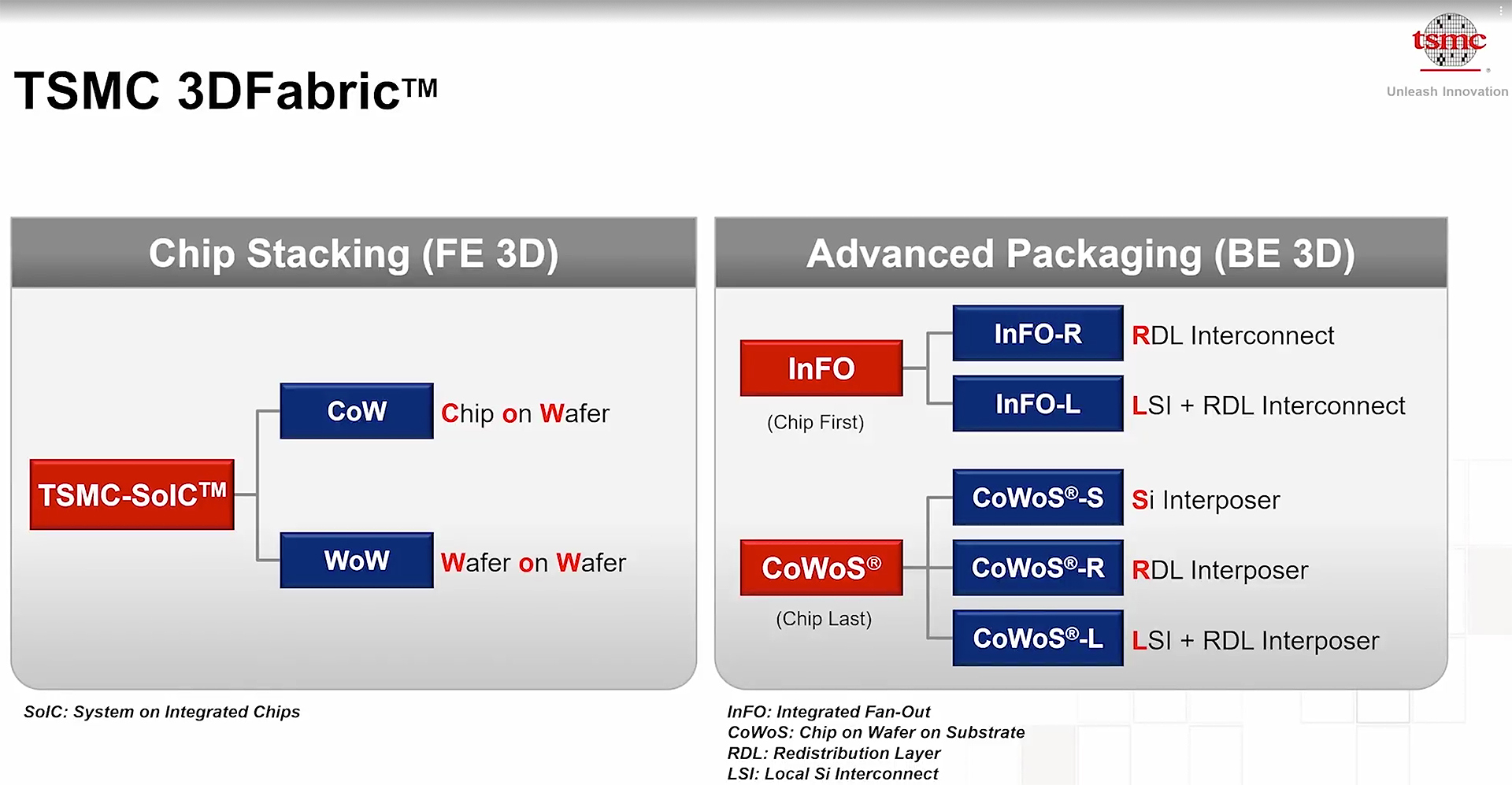

TSMC has also begun implementing strategic changes, such as redistributing some of its InFO production capacity from its northern Taiwan site in Longtan to its Southern Taiwan Science Park (STSP). It's also fast-tracking the expansion of the Longtan site. Furthermore, TSMC is increasing its in-house CoWoS production while outsourcing part of its oS manufacturing to other assembly and test (OSAT) companies. For instance, Siliconware Precision Industries (SPIL) has been one of the beneficiaries of this outsourcing initiative.

TSMC opened its Advanced Backend Fab 6 facility last week. It is set to expand its advanced packaging capacity for its frontend 3D stacking SoIC (CoW, WoW) technologies and backend 3D packaging methods (InFO, CoWoS). For now, the fab is ready for SoIC. The Advanced Backend Fab 6 can process around one million 300-mm wafers per year and carry out over 10 million hours of testing annually, with cleanroom space that is larger than the combined cleanroom spaces of all other TSMC advanced packaging facilities.

Among the most impressive features of the Advanced Backend Fab 6 is the extensive five-in-one intelligent automated material handling system. The system controls the production flow and detects defects instantly, increasing yield. This is crucial for complex multi-chiplet assemblies like AMD's MI300, as packaging defects immediately render all chiplets unusable, leading to significant losses. With data processing capabilities 500 times faster than average, the facility can maintain comprehensive production records and track every die it processes.

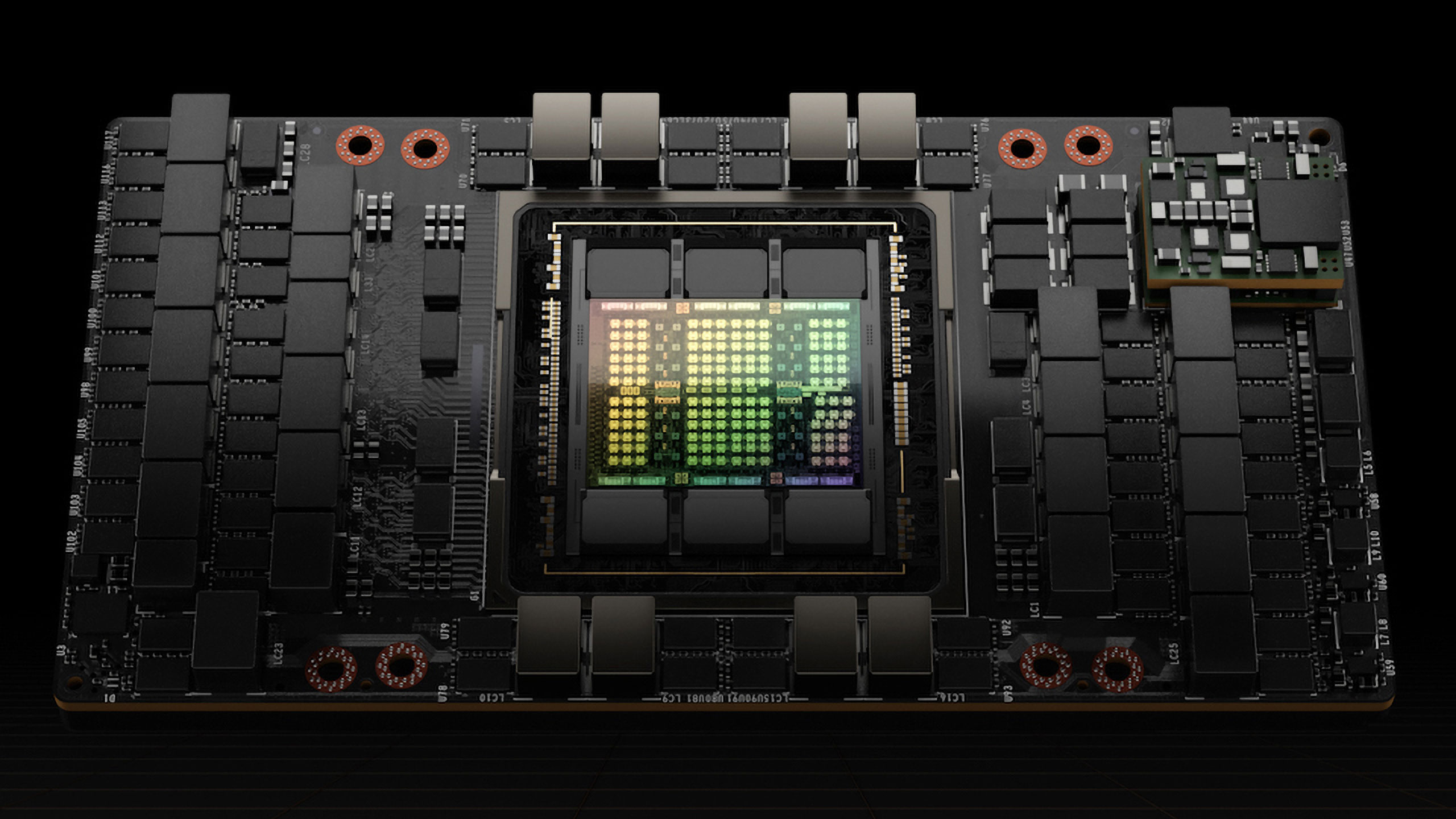

Nvidia uses CoWoS for its highly successful A100, A30, A800, H100, and H800 compute GPUs. AMD's Instinct MI100, Instinct MI200/MI200/MI250X, and the upcoming Instinct MI300 also use CoWoS.