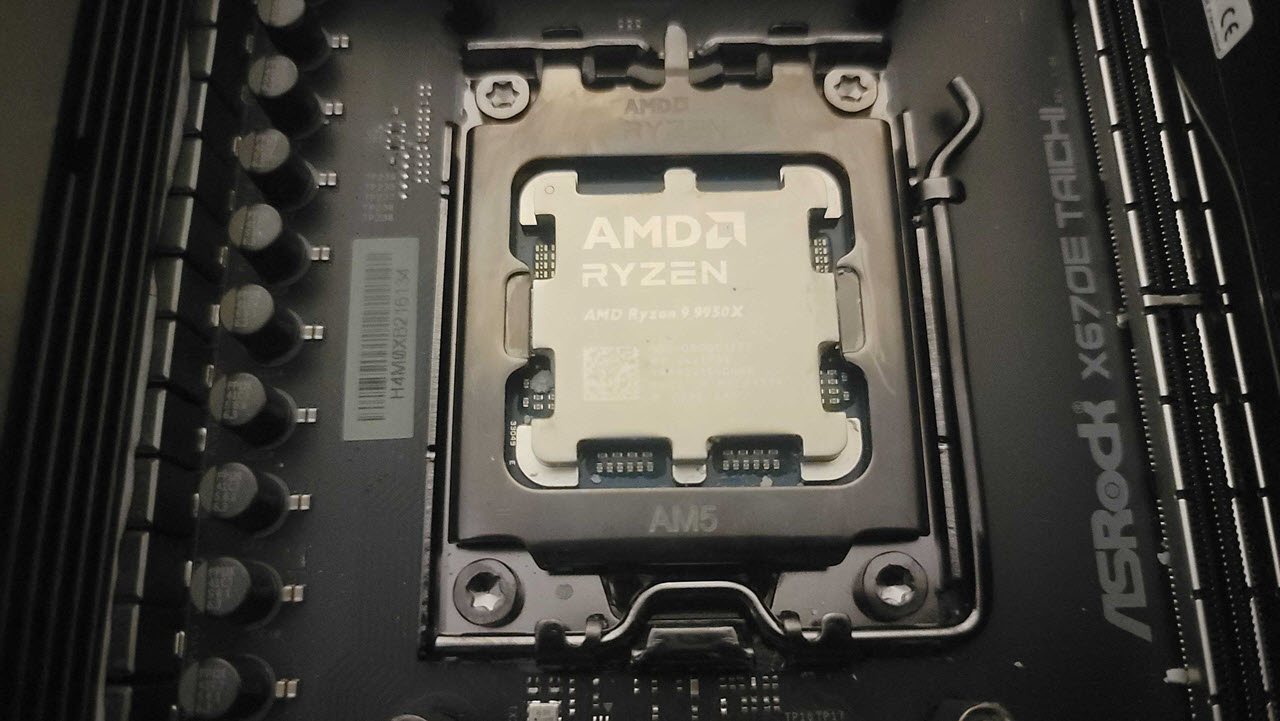

Ryzen 9000 launched with unexpectedly high cross-CCD latency on the dual-CCD models — Ryzen 9 9900X and Ryzen 9 9950X. However, AMD has now rectified the issue with a new AGESA microcode update that cuts the Ryzen 9 9900X and Ryzen 9 9950X's cross-CCD latency in half. User domdtxdissar on the Overclock forums discovered that AGESA microcode update 1.2.0.2 improves performance and cross-CCD latency from 180 ns to 75 ns.

The new microcode update lowers Ryzen 9000's cross-CCD latency to almost identical latencies as the previous generation Ryzen 9 7950X and Ryzen 9 7900X. It is unknown how precisely this change will improve performance, but the Overclock forum user reported that it does improve performance in some form. Inevitably, this change will enhance the performance of latency-sensitive applications that take advantage of multiple CPU cores on Ryzen 9000 chips with a dual-CCD configuration.

This change will most likely not affect gaming because AMD has implemented the same scheduling driver on its Ryzen 7950X3D and 7900X3D chips to its Ryzen 9 9950X and 9900X CPUs. This scheduler will prevent games from utilizing both CCDs simultaneously to maximize performance and minimize system latency.

Multiple outlets discovered Zen 5's oddly long cross-CCD latency when the Ryzen 9 9950X and 9900X first launched. Sister site AnandTech was entirely surprised when it found significantly higher multi-CCD latencies than Zen 4, noting that nothing changed in the architecture to warrant such behavior—Ryzen 9000 uses the same IOD and Infinity Fabric configuration as Ryzen 7000.

However, these latency changes were not created without cause. According to Y-Cruncher author Alexander Yee (sourced from Reddit), one of AMD's architects revealed that the high latency regression in Zen 5 resulted from new tuning parameters they implemented to help boost performance in workloads the company was testing against. The only problem with AMD's tuning was that it did not reportedly account for synthetic benchmarks, which created the high core-to-core latencies seen on latency-sensitive benchmarks.

Zen 5's cross-CCD latency optimizations also reportedly took a long time to develop due to testing and validation, which is why we only see them now. Thankfully, it appears AMD's latency problems were mostly related to synthetic benchmarks, so there's a good chance we won't see significant performance variance with this new AGESA update in regular multi-threaded workloads.