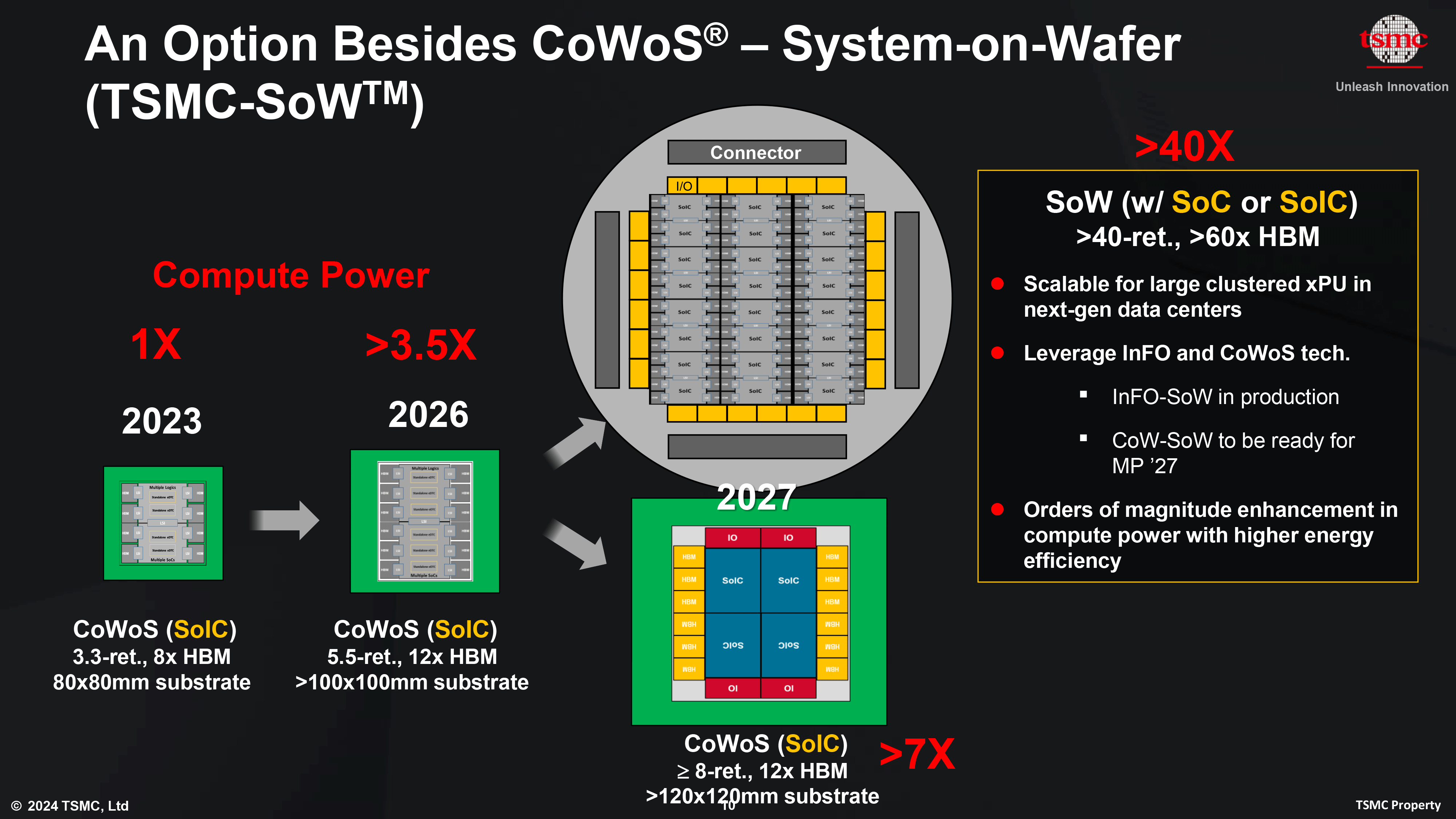

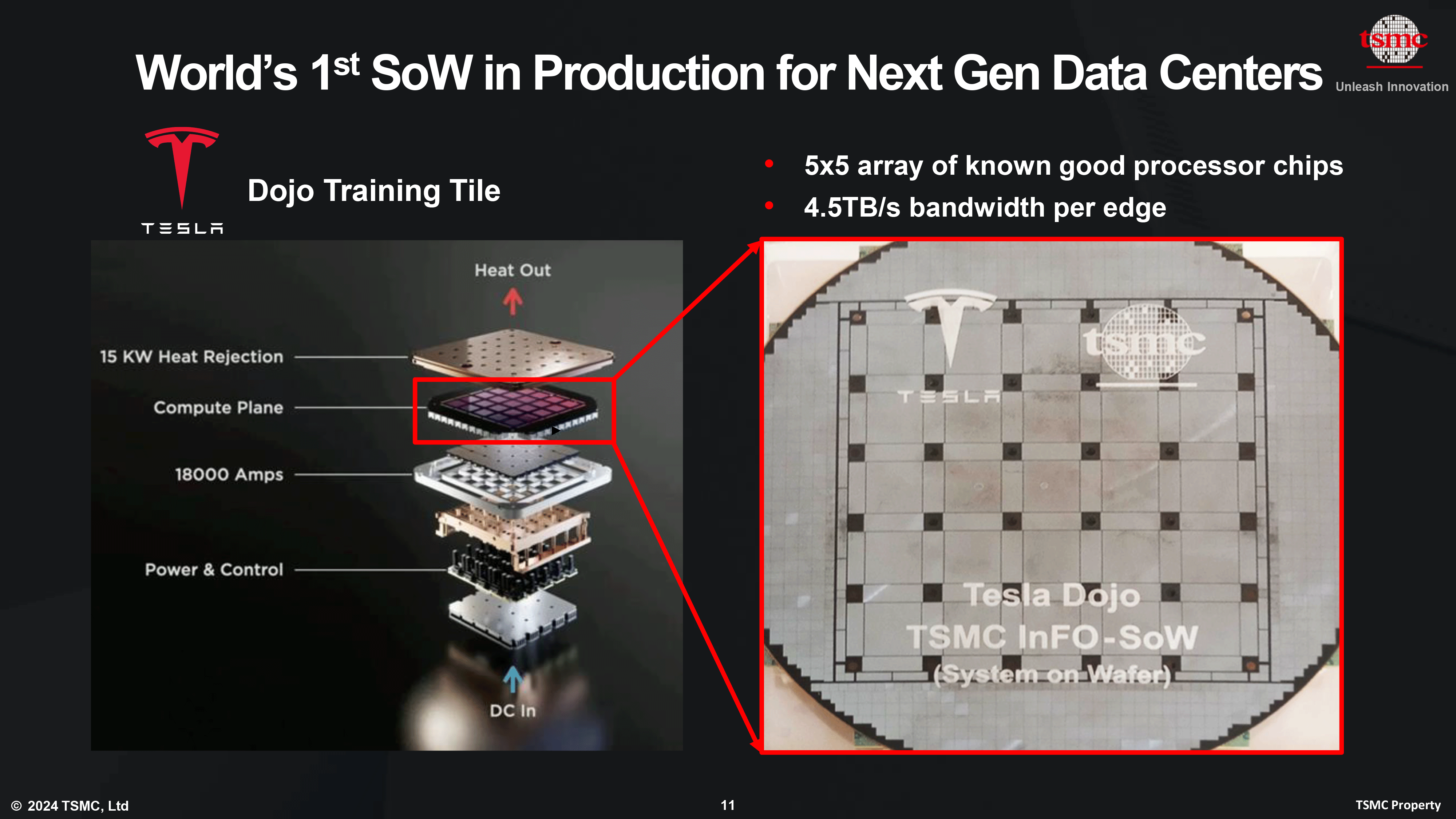

TSMC is taking the wafer-scale fabrication battle into the third dimension with a new technology. At its North American Technology Symposium, it introduced its next-generation system-on-wafer platform—CoW-SoW—that will enable 3D integration with wafer-scale designs. This builds on the InFO_SoW system-on-wafer integration technology technology that TSMC introduced in 2020 that allows it to build wafer-scale logic processors. So far, only Tesla has adopted this tech for its Dojo supercomputer, which TSMC says is now in production

In its forthcoming CoW-SoW platform, TSMC is set to merge two of its packaging methods — InFO_SoW and System on Integrated Chips (SoIC) — in its system-on-wafer platform. By using the Chip-on-Wafer (CoW) technology, this method will enable the stacking of memory or logic directly atop a system-on-wafer. The new CoW_SoW technology is expected to be ready for large-scale production by 2027, though it remains to be seen when actual products arrive on the market.

"So, in the future, using wafer-level integrations [will allow] our customers to integrate even more logic and memory together," said Kevin Zhang, Vice President of Business Development at TSMC. "SoW is no longer a fiction; this is something we already work with our customers [on] to produce some of the products already in place. We think by leveraging our advanced wafer-level integration technology, we can provide our customer a very important path that allows them to continue to grow their capability to bring in more computation, more energy efficient computation, to their AI cluster or [supercomputer]."

Currently, TSMC's CoW-SoW focuses on integrating wafer-scale processors with HBM4 memory. These next-generation memory stacks will feature a 2048-bit interface, which will make it feasible to integrate HBM4 directly on top of logic chips. Meanwhile, it may also make sense to stack additional logic on wafer-scale processors to optimize costs.

Wafer-scale processors in general (i.e., Cerebras's WSE), and InFO_SoW-based processors in particular, offer significant performance and efficiency benefits, including high-bandwidth and low-latency core-to-core communications, low power delivery network impedance, and high energy efficiency. As an added bonus, such processors also have additional redundancy in the form of 'extra' cores.

However, the InFO_SoW technology has certain limitations. For instance, wafer-scale processors made using this method rely entirely on on-chip memory, which may fall short for future AI needs (but is good for now). CoW-SoW will solve this, as it will allow putting HBM4 on such wafers. In addition, InFO_SoW wafers are processed using a single node, and this node does not support 3D stacking, which will be supported by CoW-SoW products.