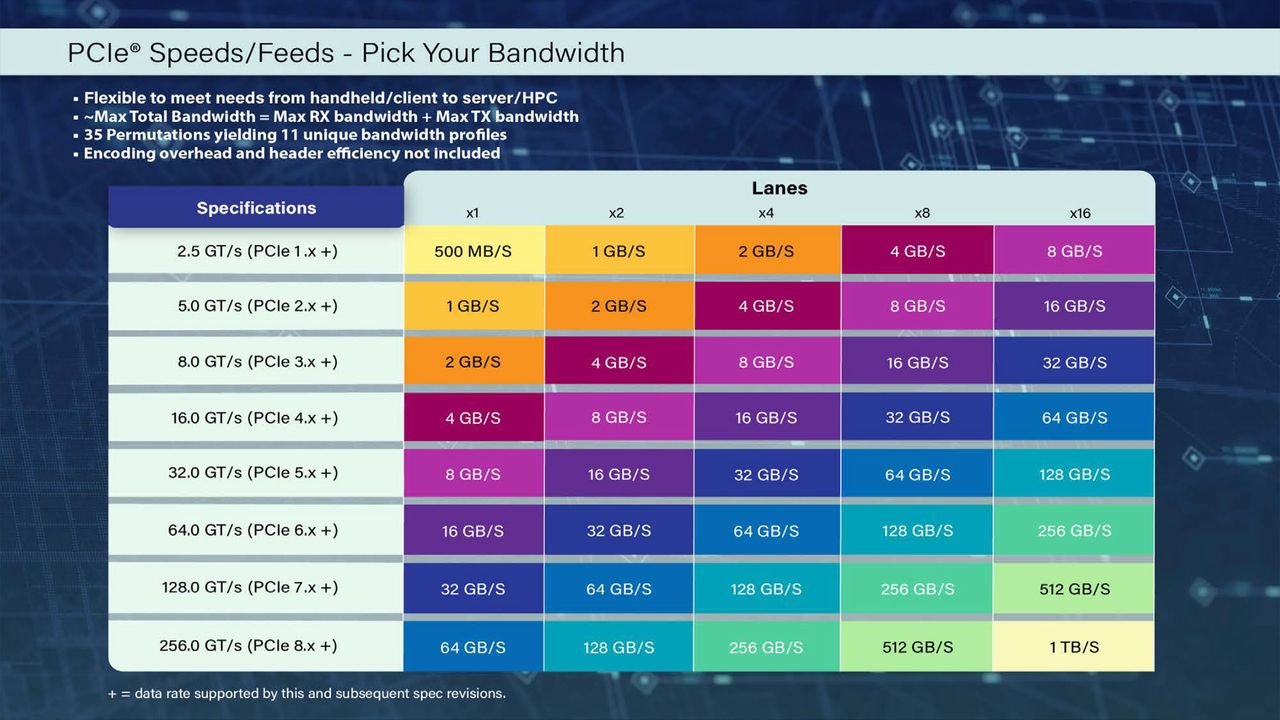

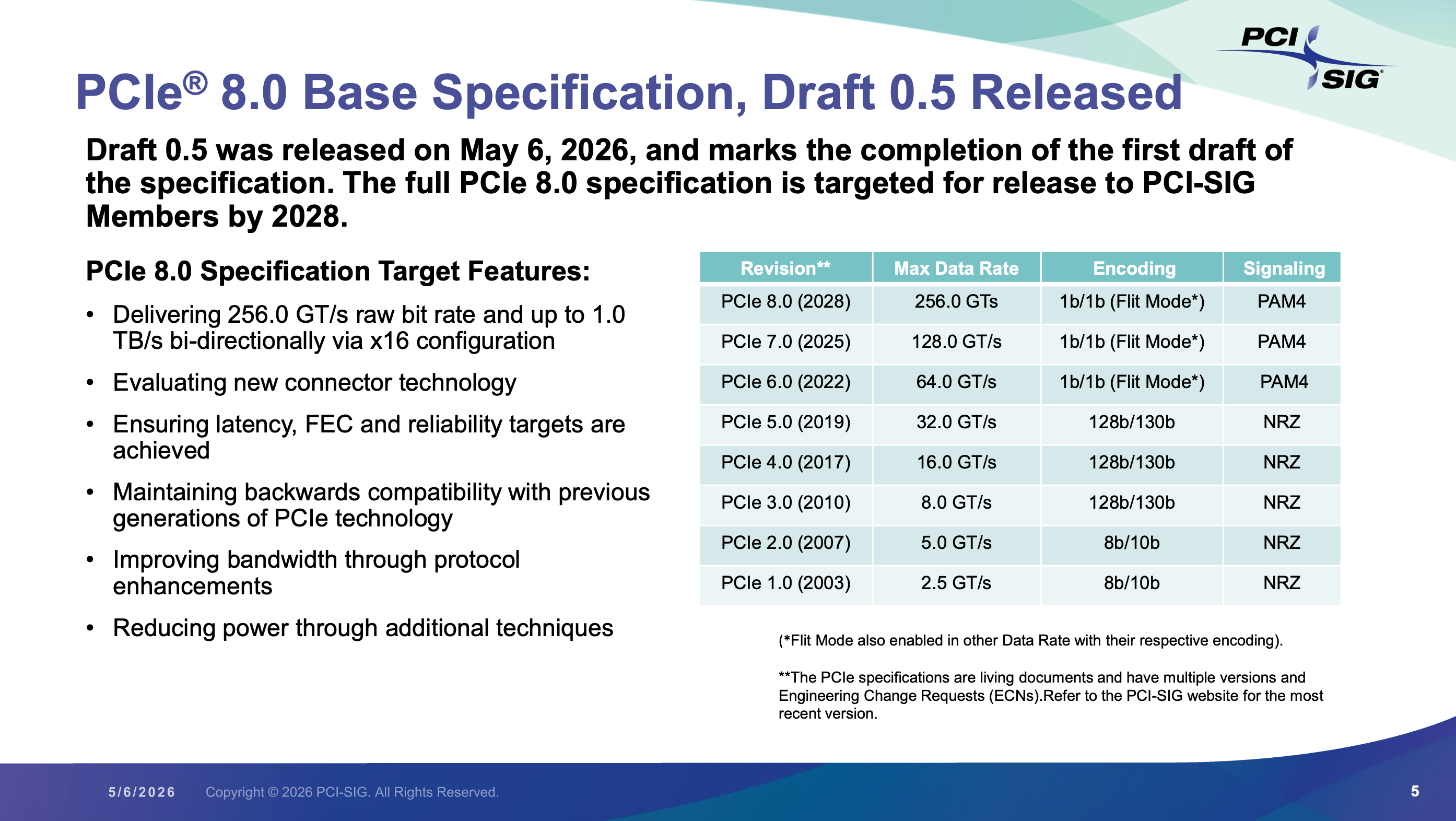

The PCI-SIG, the organization that oversees development of PCIe and adjacent standards, on Wednesday announced the availability of the PCIe 8.0 draft specification version 0.5, a major milestone. The first draft of the specification sets the architectural requirements and is designed to enable PCI-SIG members to start prototyping and submit their final proposals. Version 0.5 of the specification maintains that the transfer rate supported by the new interconnection will reach 256 GT/s, enabling up to 1 TB/s bi-directional bandwidth via an x16 configuration.

Version 0.5 of the PCIe standard is the first full draft of the spec that locks in key conceptual targets and mechanisms, and outlines all major aspects of the architecture, including electrical, logical, compliance, and software. This means that PCI-SIG maintains a target bit rate of 256 GT/s; PAM4 signaling with forward error correction (FEC) and Flit Mode encoding; bandwidth-improving protocol enhancements; backward compatibility; and new connector technology that is now being evaluated. Meanwhile, since version 0.5 is not the final draft and not all parts of the specification are frozen, some electrical parameters and protocol optimizations can be tuned further.

The new release is a major milestone as this is when hardware designers — large companies like AMD, Intel, and Nvidia, as well as IP or PHY vendors — may start early prototyping and architecture work, albeit with contingency plans for possible changes. The most important point is that the specification is mature enough, and development work can begin.

One of the intriguing parts of the announcement is that PCI-SIG continues to evaluate new connector technology, which essentially means the current copper physical layer is getting uncomfortably close to its limits.

Loss budgets, crosstalk, and reflections have become serious constraints for PCIe 5.0 and 6.0, but with PCIe 8.0 and its 256 GT/s bit rate — a data transfer rate no copper-based standard has ever achieved — they are likely going to become a nightmare. At such speeds, the traditional edge connector and motherboard routing may not deliver acceptable signal integrity without excessive power (for equalization) or latency (for FEC). As a result, PCI-SIG might look to redesign PCIe slots with better materials and tighter tolerances, or to shorten electrical paths once again while increasing the number of redrivers per link. In any case, since PCI-SIG wants to maintain backward compatibility, do not expect any drastic changes on the connector level.

With this draft available, the PCIe 8.0 standard continues to progress toward final ratification in 2028.