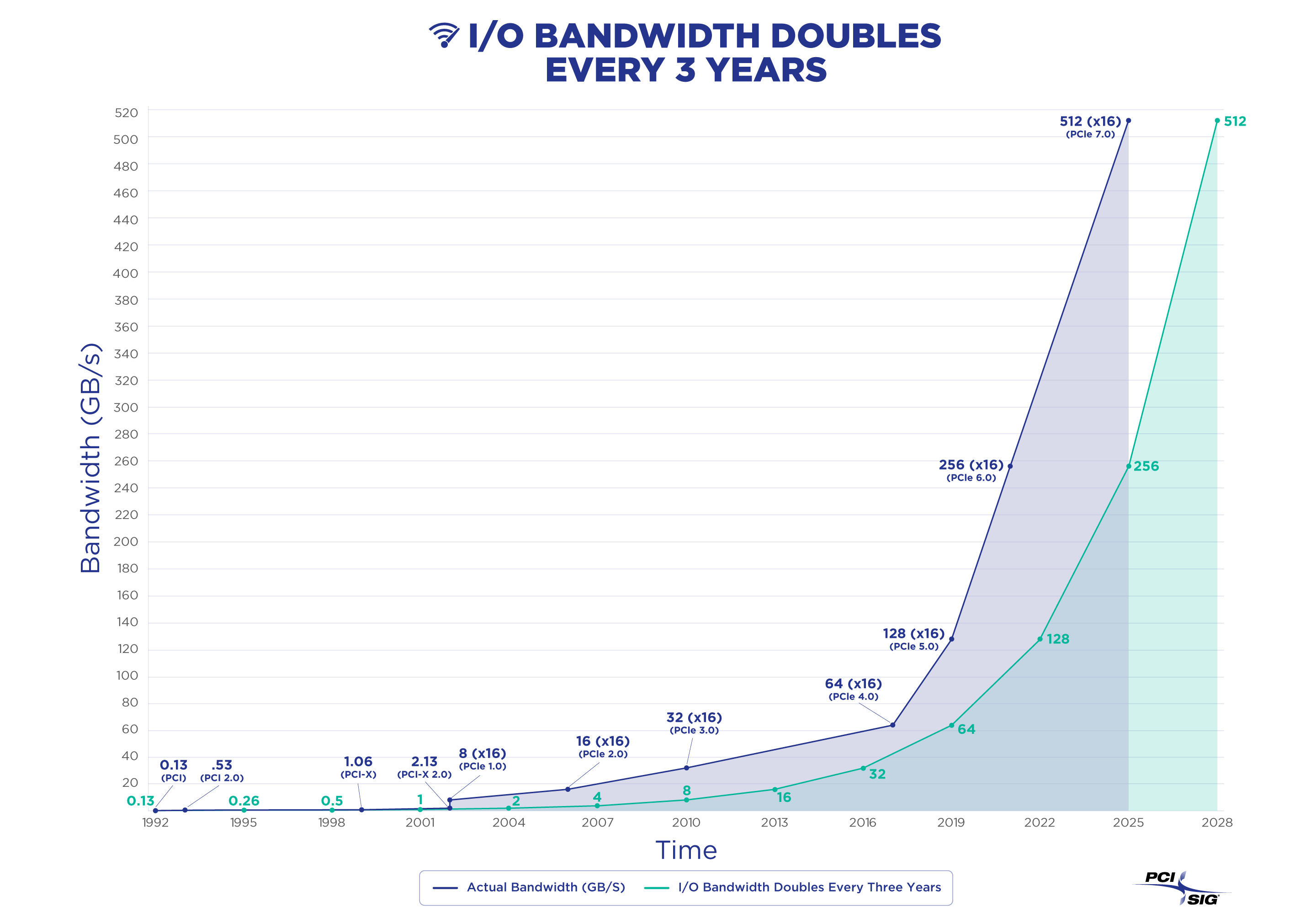

PCI-SIG on Tuesday published version 0.3 of the PCI Express 7.0 specification, marking a significant achievement for the technology that will increase the PCIe data transfer rate to 128 GT/s. This preliminary release indicates that members of the organization have agreed on the key features and architecture of the upcoming technology.

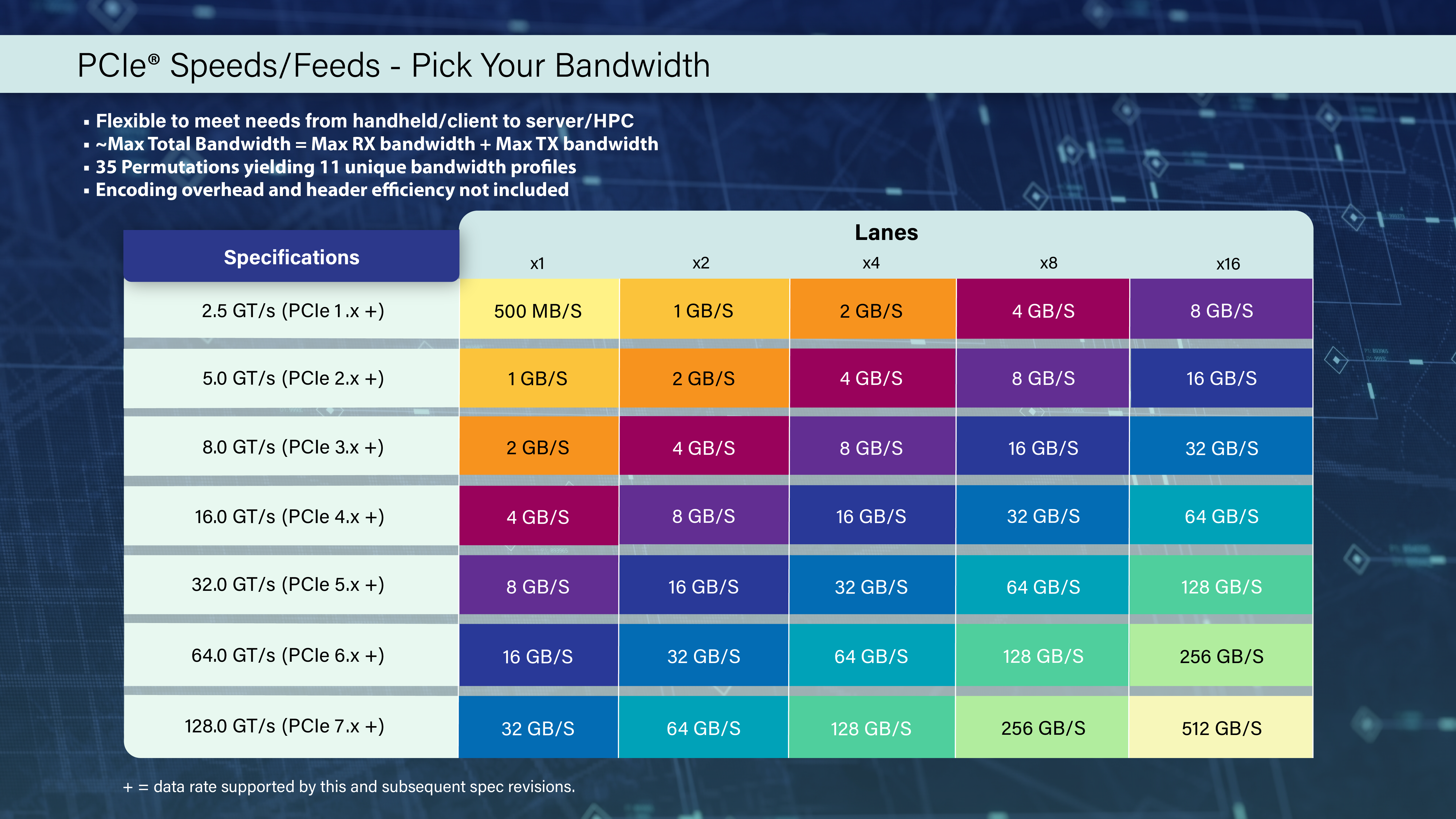

PCIe 7.0 is set to enhance the data transfer speed to 128 GT/s for each pin, substantially improving the 64 GT/s in PCIe 6.0 and the 32 GT/s in PCIe 5.0. This implies a 16-lane (x16) connection can support a bi-directional bandwidth of 512 GB/s before considering the encoding overhead. In a bid to increase data transfer rate and bandwidth, the PCIe Gen7 interface is set to use pulse amplitude modulation with four levels (PAM4) signaling, 1b/1b flit mode encoding, and forward error correction (FEC), which are features that the standard inherits from PCIe Gen6.

PCI-SIG has a very precise specification development process consisting of several releases/checkpoints. Version 0.3 typically lacks specifics, yet it provides an overview of the intended objectives and how to achieve them. Concerning PCIe 7.0, the primary targets include a data transfer rate of 128 GT/s and physical solutions that would ensure reliable and energy-efficient data transmission at this rate.

While we know the technology will rely on PAM4, flit mode, and FEC, specifics about PCIe Gen7 implementation look particularly interesting. The shift to PCIe 7.0, like previous transitions to PCIe 4.0 and 5.0, will necessitate shorter PCIe traces because of the increased signaling speeds. This will reduce the permissible distance between root and endpoint devices such as CPUs and expansion cards (graphics cards, accelerators, SSDs, network cards) without components like retimers. For now, we know that implementing PCIe Gen5 requires thicker PCBs and higher-quality materials, which means higher costs and prices. Yet, we have no idea about cost considerations for PCIe Gen7 in this regard.

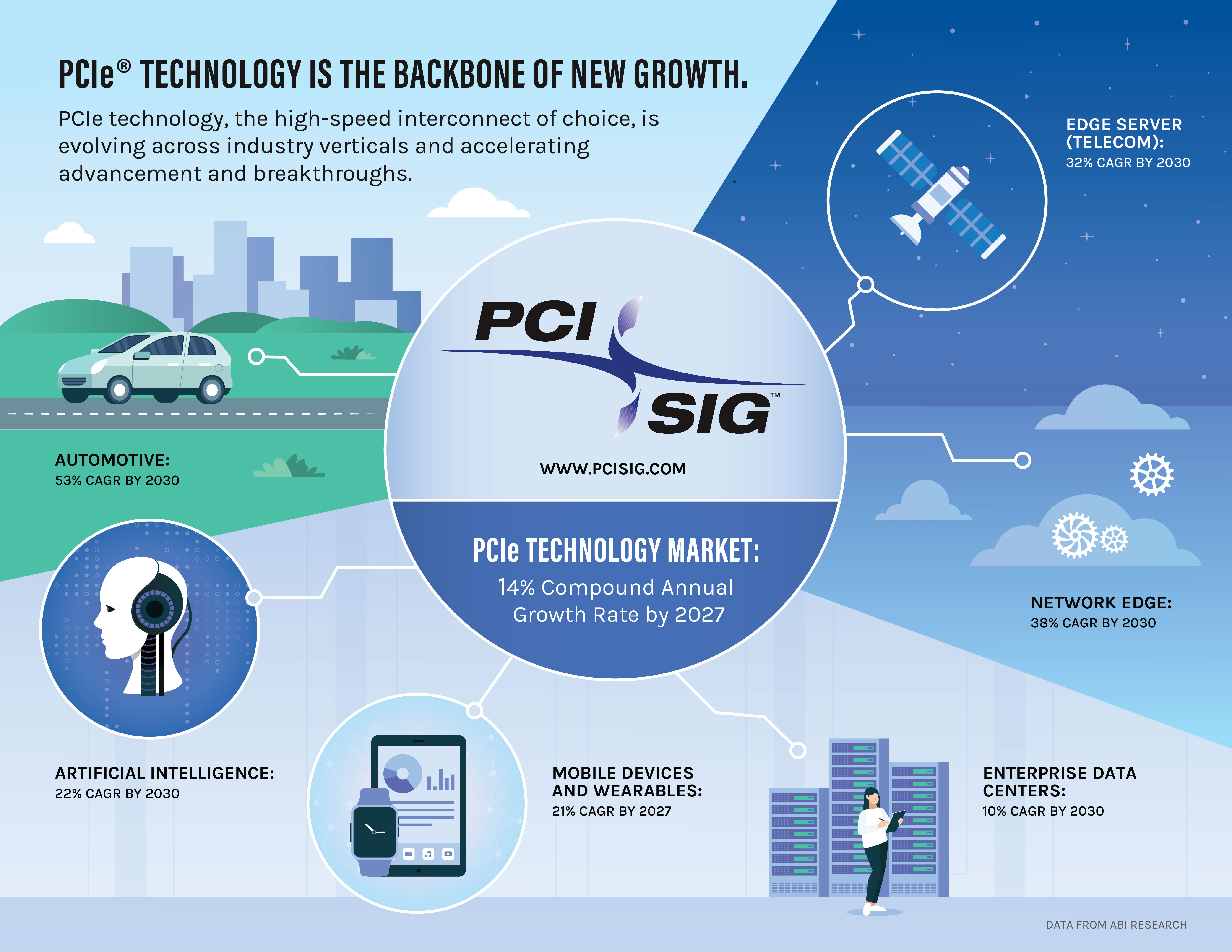

It should be noted that PCI-SIG itself clearly states that it is developing PCIe 7.0 to support such bandwidth-hungry applications as 800G Ethernet, AI/ML, cloud and quantum computing, hyperscale datacenters, HPC, edge, and aerospace/military. While we are sure that PCIe 7.0 will eventually end up in client PCs, PCI-SIG never mentions desktops or laptops.

"PCI Express technology leads the industry as a foundational I/O interconnect and can be found in everything from automobiles to data center servers," said PCI-SIG President Al Yanes. "As PCIe architecture speed increases, we will continue to expand our traditional verticals while expanding into exciting new verticals to meet the demand for a high-bandwidth, low-latency interconnect."