Unofficial information that Intel's upcoming codenamed Meteor Lake processor is set to feature L4 cache has been floating around for some time now. Now, a new Intel patent found by VideoCardz indicates that Intel has prepped a codenamed Adamantine L4 cache tile that it may use for some CPUs. This IC could compete against AMD's 3D V-Cache in certain applications, but the chiplet will not be used solely as a performance booster.

Typically, caches serve to increase the performance of the memory subsystem by rapidly providing compute cores with necessary data. But there are other use cases too, as large caches can store a lot of data. The patent suggests that Intel's Adamantine (or ADM) cache can improve communication not only between the CPU and memory but also between the CPU and security controller. For example, the L4 can be used to improve boot optimization and even preserve data from caches at reset to improve loading times.

Windows 10 and Windows 11 loading times are fairly quick on Intel's platforms even today. But Intel believes that with memory available at reset, faster and more efficient BIOS solutions can be developed for modern devices like car infotainment systems and household robots. Automotive and robotic designs closely link SoC security with firmware phases, ensuring platform security. Failing to follow recommendations stops the platform from booting to the OS, thus reducing attack risks and protecting confidential blocks, which is crucial for cars and robots.

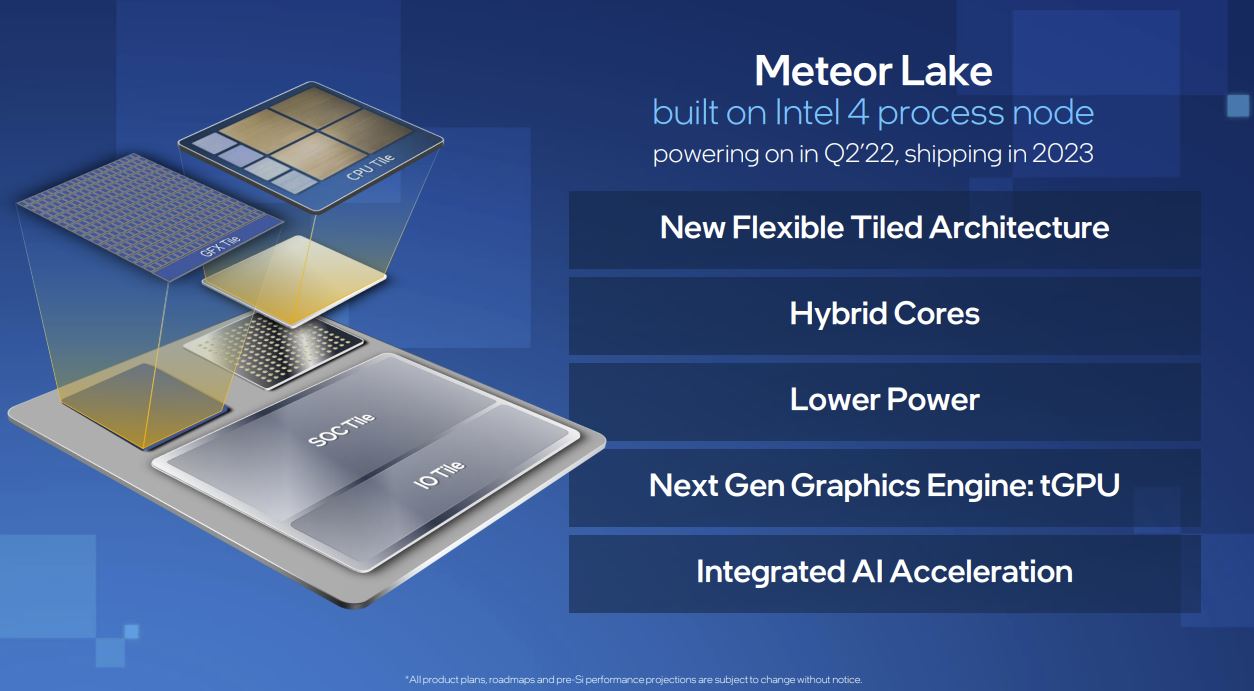

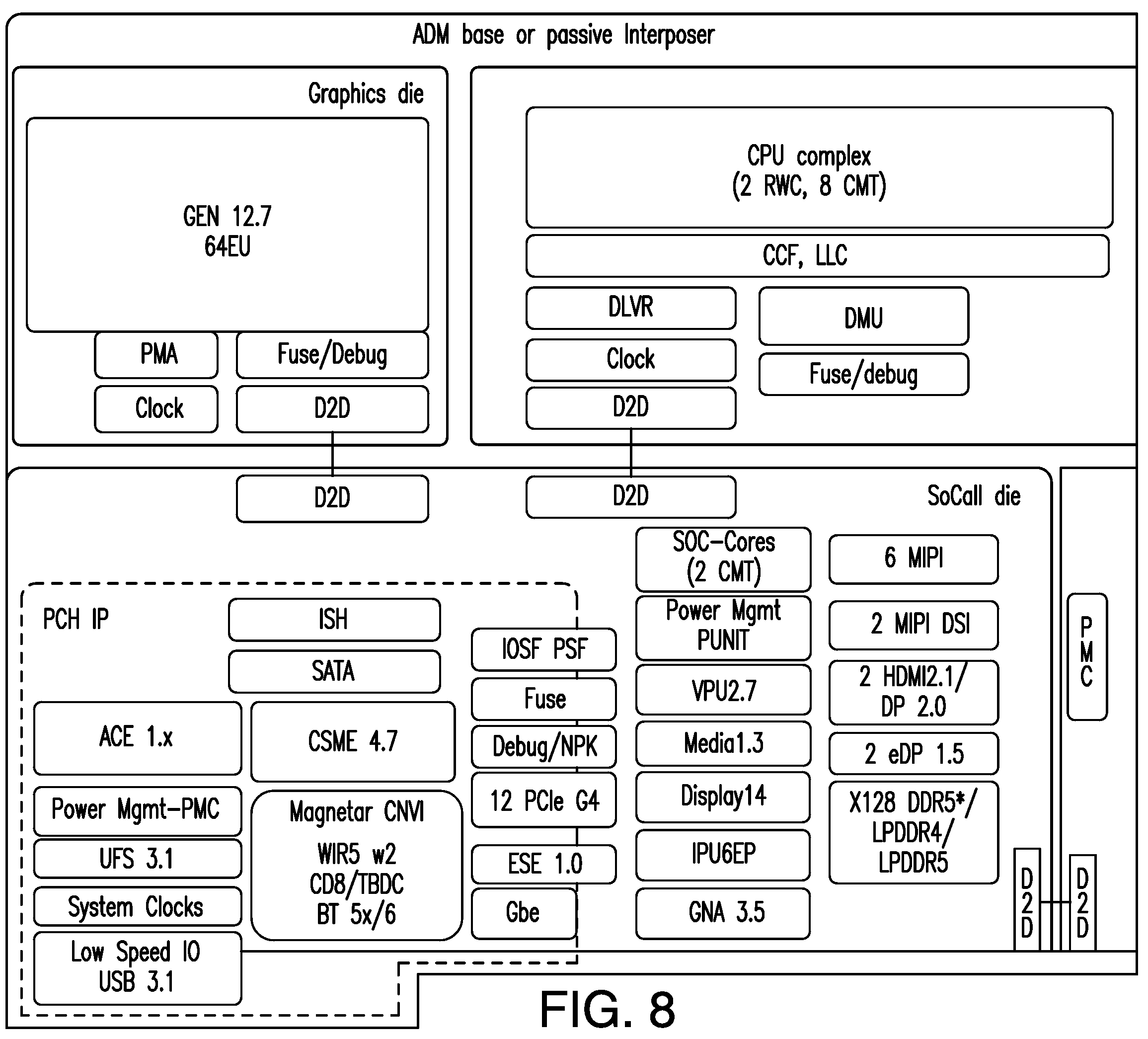

While the patent itself does not mention Meteor Lake, images supplied with it clearly demonstrate a processor with two high-performance Redwood Cove and eight energy-efficient Crestmont cores on one tile produced on Intel 4 fabrication process, a graphics chiplet based on Intel's Gen 12.7 architecture (Xe-LPG), an SoC tile containing two more Crestmont cores, and an I/O chiplet interconnected using Intel's Foveros 3D technology. The description corresponds to that of Intel's Meteor Lake processor. Meanwhile, the Adamantine L4 cache can be used for a wide array of applications beyond Meteor Lake.

Here is Intel's description of Adamantine:

Next generation client SoC architectures may introduce large on-package caches, which will allow novel usages. Access time for the L4 (e.g., "Adamantine" or "ADM") cache may be much less than the DRAM access time, which is used to improve host CPU and security controller communications. Embodiments help to protect innovations in boot optimization. Value is added for high end silicon with higher pre-initialized memory at reset, potentially leading to increased revenue. Having memory available at reset also helps to nullify legacy BIOS assumptions and make a faster and efficient BIOS solution with a reduced firmware stage (e.g., pre-CPU reset stage, IBBL stage and IBB stage) for modern device use cases like Automotive IVI (in-vehicle infotainment, e.g., turn on rear view camera within 2 sec), household and industrial robots, etc. Accordingly, new market segments may be available. [0059] Embodiments are able to tightly couple SoC key security recommendations with firmware mandatory phases (e.g., IBBL and/or IBB) specially enfolded with SoC provided at the silicon initialization binary (e.g., FSP-M) to ensure that the platform is always adhering to SoC recommendations. Failures to do so by skipping FSP-M will not permit the platform to boot to the OS. Such an approach eventually reduces the attack surface and provides passive way to protect confidential functional blocks (e.g., intellectual property blocks/IPs).