A Stanford University researcher is studying a technology that could drastically improve the performance of internal caches in modern-day CPUs and GPUs. This technology is known as hybrid gain cell memory (Blocks and Files reports), which combines features from SRAM and DRAM to primarily boost storage density.

According to the lead member of the research team, Stanford Professor of Electrical Engineering Philip Wong, there is a "memory wall problem" with a GPU's built-in SRAM-based cache that has to be loaded with data from comparatively slow DRAM. This transition purportedly takes too much time and electrical energy, making a successor for traditional SRAM with better performance properties something to be desired.

Capacity issues are also becoming a limiting factor with SRAM. SRAM purportedly takes up quite a large area on modern-day chips, needing four transistors to store a bit and two to control cell access. DRAM, by contrast, requires just a single transistor and some additional components to do the same thing. However, DRAM also suffers from issues such as constantly needing to refresh the data stored on each chip.

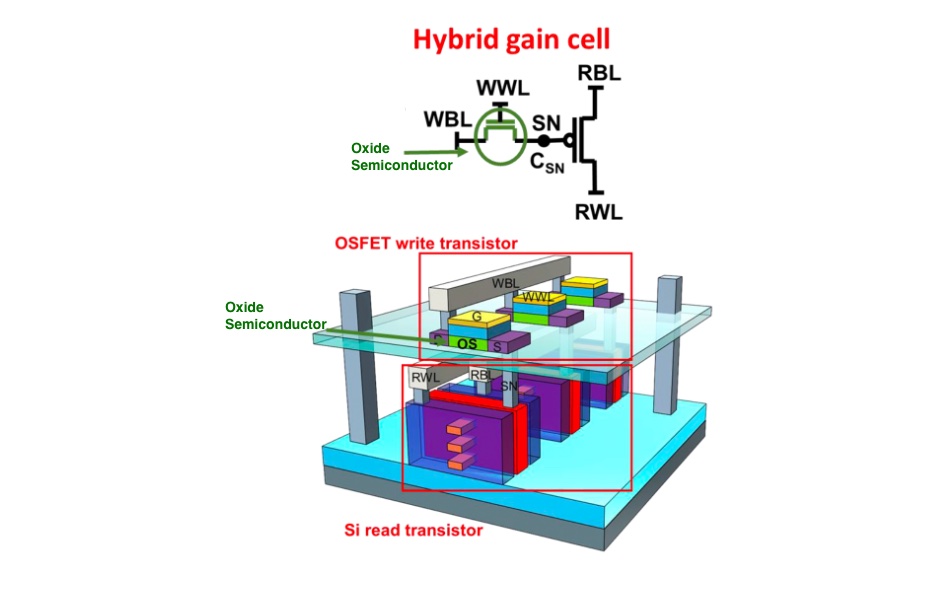

Hybrid gain cell technology aims to provide the best of both technologies in a single solution. The main attribute of the gain cell is its integration of separate read and write transistors for storing data, removing the requirement of an extra capacitor, which DRAM needs to function.

Wong's research team's tech uses a hybrid gan cell with two transistors made with different materials. Atomic layer deposition indium tin oxide (ALD ITO) is used for the write transistor, and a silicon P-channel metal-oxide-semiconductor (Si PMOS) is used for the read transistor. This was a more performant solution than two silicon oxide-based transistors, which purportedly had slow bit-state signal readings.

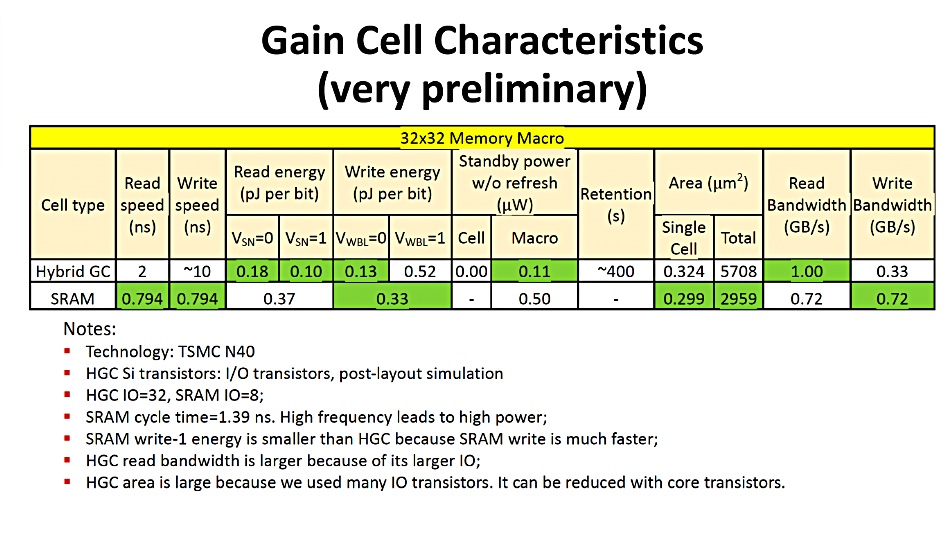

The Standford University research team discovered excellent performance traits with hybrid gain cell technology. In testing, a gain cell-powered device could store data for over an hour. This is miles better than anything DRAM can do, which needs to be refreshed every 64ms. Data could also be read up to 50x faster than DRAM from an OS-OS transistor gain sell with a 1 to 10ns access time.

However, this doesn't necessarily translate into better real-world performance. The team's gain cell technology can purportedly be slower than SRAM in some performance aspects, specifically for gain cell configurations with higher data density than SRAM.

Regardless, the most crucial trait of gain cell memory is its higher storage capacity ceiling, which is very important for low-level caches. Bigger caches result in less time for the CPU or GPU to transfer data from system DRAM, boosting performance and latency. This is the underlying principle behind AMD's 3D V-Cache technology.

The team's gain cell technology could be used in future CPUs and GPUs, potentially boosting low-level cache capacities beyond what we see today. There's also nothing stopping Intel or AMD from utilizing 3D variants of this tech to increase capacity even further than today's 3D-based caches.

.png?w=600)